### **General Description**

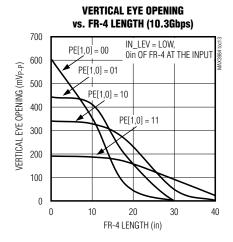

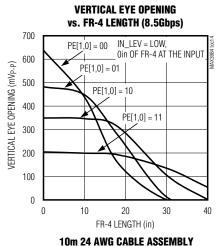

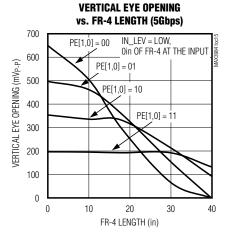

The MAX3984 is a single-channel, preemphasis driver with input equalization that operates from 1Gbps to 10.3Gbps. It provides compensation for copper links, such as 8.5Gbps Fibre Channel and 10.3Gbps Ethernet, allowing spans of up to 10m with 24 AWG cable. The driver provides four selectable preemphasis levels, and the selectable input equalizer compensates for up to 10in of FR-4 circuit board material at 10Gbps.

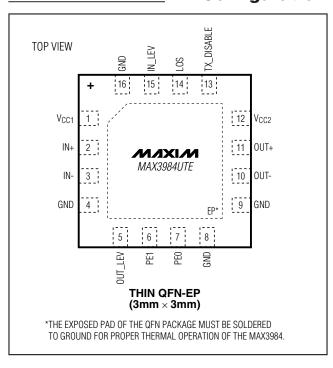

The MAX3984 also features SFP-compliant loss-of-signal (LOS) detection and TX\_DISABLE. Selectable output swing reduces EMI and power consumption. The MAX3984 is packaged in a lead-free, 3mm x 3mm, 16-pin thin QFN and operates from a 0°C to +85°C temperature range.

### **Applications**

8.5Gbps Fibre Channel Active Cable Assemblies

10.3Gbps Ethernet STM-64

Pin Configuration appears at end of data sheet.

## \_\_\_\_\_Features

- ♦ Drives Up to 10m of 24 AWG Cable

- ♦ Drives Up to 30in of FR-4

- ♦ Selectable 1000mV<sub>P-P</sub> or 1200mV<sub>P-P</sub> Differential Output Swing

- ♦ Selectable Output Preemphasis

- ♦ Selectable Input Equalization

- ♦ LOS Detection with Built-In Squelch

- **♦ Transmit Disable**

- ♦ Hot Pluggable

### **Ordering Information**

| PART        | TEMP<br>RANGE | PIN-PACKAGE     | PKG<br>CODE |

|-------------|---------------|-----------------|-------------|

| MAX3984UTE+ | 0°C to +85°C  | 16 Thin QFN-EP* | T1633F-3    |

<sup>+</sup>Denotes a lead-free package.

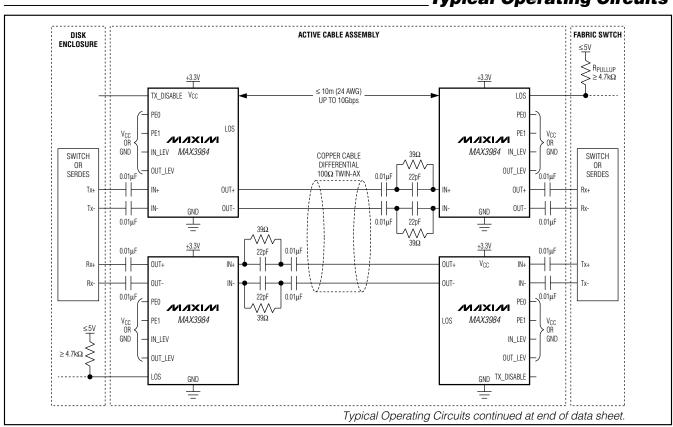

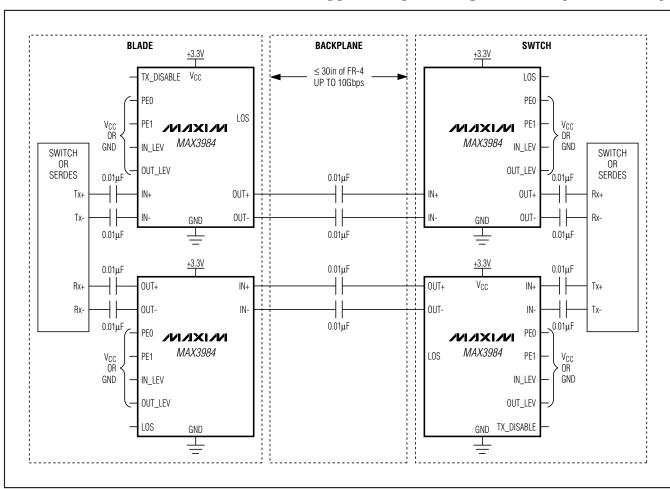

### **Typical Operating Circuits**

<sup>\*</sup>EP = Exposed pad.

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage Range (VCC)      | 0.5V to +4.1V             |

|---------------------------------|---------------------------|

| Continuous Output Current Range |                           |

| (OUT+, OUT-)                    | 25mA to +25mA             |

| Input Voltage Range (IN+, IN-)  | 0.5V to $(V_{CC} + 0.5V)$ |

| Logic Inputs Range (PE1, PE0,                                |

|--------------------------------------------------------------|

|                                                              |

| TX_DISABLE, IN_LEV, OUT_LEV)0.5V to (V <sub>CC</sub> + 0.5V) |

| LOS Open-Collector Supply Voltage Range                      |

| (with $\geq 4.7 k\Omega$ pullup)0.5V to +5.5V                |

| Storage Ambient Temperature Range (TSTG)55°C to +150°C       |

|                                                              |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **OPERATING CONDITIONS**

| PARAMETER                                                         | SYMBOL | CONDITIONS                                                  | MIN | TYP | MAX  | UNITS               |

|-------------------------------------------------------------------|--------|-------------------------------------------------------------|-----|-----|------|---------------------|

| Supply Voltage                                                    | Vcc    |                                                             | 3.0 | 3.3 | 3.6  | V                   |

| Supply Noise Tolerance                                            |        | 1MHz≤f<2GHz                                                 |     | 40  |      | mV <sub>P-P</sub>   |

| Operating Ambient Temperature                                     | TA     |                                                             | 0   | 25  | 85   | °C                  |

| Bit Rate                                                          |        | NRZ data                                                    | 1.0 | 8.5 | 10.3 | Gbps                |

| Consecutive Identical Digits (CID)                                |        | CID (bits)                                                  |     |     | 100  | Bits                |

|                                                                   |        | IN_LEV = high, Figure 2;<br>4.25Gbps < data rate ≤ 10.3Gbps | 360 |     | 1200 |                     |

| Input Swing (Measured differentially at data source,              |        | IN_LEV = high, Figure 2;<br>1.25Gbps < data rate ≤ 4.25Gbps | 360 |     | 1600 | m)/a a              |

| point A of Figure 2 and 3. Pins LOS and TX_DISABLE are floating.) |        | IN_LEV = high, Figure 2;<br>1.0Gbps ≤ data rate ≤ 1.25Gbps  | 360 |     | 2400 | - mV <sub>P-P</sub> |

|                                                                   |        | IN_LEV = low, Figure 3;<br>1.0Gbps < data rate ≤ 10.3Gbps   | 100 |     | 360  |                     |

| Time to Reach 50%<br>Mark/Space Ratio                             |        |                                                             |     |     | 1    | μs                  |

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0V \text{ to } +3.6V, T_A = 0^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}. \text{ Typical values are at } T_A = +25^{\circ}\text{C}, V_{CC} = +3.3V, \text{ unless otherwise noted.})$

| PARAMETER                                                                 | SYMBOL                          |                                                    | CONDITION      | NS         |      | MIN  | TYP               | MAX  | UNITS             |

|---------------------------------------------------------------------------|---------------------------------|----------------------------------------------------|----------------|------------|------|------|-------------------|------|-------------------|

| Cura al v. Curra ant                                                      | 1                               | OUT_LEV = low                                      | , TX_DISAE     | BLE = low  |      |      | 100               | 124  |                   |

| Supply Current                                                            | Icc                             | OUT_LEV = hig                                      | h, TX_DISA     | BLE = low  | /    |      | 120               | 148  | mA                |

| Inrush Current                                                            |                                 | Beyond steady                                      | (Note 1)       |            |      | 10   | mA                |      |                   |

| Power-On Delay                                                            |                                 | (Note 1)                                           |                |            |      | 1    |                   | 30   | ms                |

| <b>EQUALIZER AND DRIVE SPEC</b>                                           | IFICATIONS                      |                                                    |                |            |      |      |                   |      |                   |

| Input Return Loss                                                         | S11                             | 100MHz to 5GH                                      | 100MHz to 5GHz |            |      |      |                   |      | dB                |

| Input Resistance                                                          |                                 | Measured differentially (Note 2)                   |                |            |      | 85   | 100               | 115  | Ω                 |

| D'''                                                                      |                                 | Measured diffe<br>2; TX_DISABLE<br>PE1 = PE0 = his | E = Iow, OUT   |            |      | 1000 |                   | 1300 |                   |

| Different Output Swing (Notes 3, 4)                                       |                                 | Measured diffe<br>2; TX_DISABLE<br>PE1 = PE0 = his | E = Iow, OUT   |            |      | 800  |                   | 1100 | mV <sub>P-P</sub> |

|                                                                           |                                 | TX_DISABLE = high, PE1 = PE0 = high                |                |            |      |      |                   | 10   |                   |

| Common-Mode Output (AC)<br>(Note 4)                                       |                                 | Measured at po<br>TX_DISABLE =                     | n (Note 5)     |            |      | 25   | mV <sub>RMS</sub> |      |                   |

| Output Resistance                                                         | Rout                            | OUT+ or OUT-,                                      | single-ende    | ed         |      | 42   | 50                | 58   | Ω                 |

| Output Return Loss                                                        | S22                             | 100MHz to 5GH                                      | Ηz             |            |      |      | 12                |      | dB                |

| Output Transition Time 20% to 80%                                         | t <sub>r</sub> , t <sub>f</sub> | 20% to 80% (No                                     | ote 6)         |            |      |      | 32                | 40   | ps                |

| Random Jitter (Note 4)                                                    |                                 | Measured at po                                     | oint D in Fig  | ure 3 (Not | e 7) |      |                   | 0.8  | psRMS             |

|                                                                           |                                 |                                                    |                | PE1        | PE0  |      |                   |      |                   |

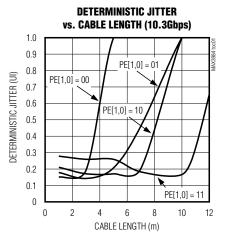

|                                                                           |                                 |                                                    |                | 0          | 0    |      | 3.5               |      |                   |

| Output Preemphasis                                                        |                                 | Figure 1 (Note 3                                   | 3)             | 0          | 1    |      | 6.5               |      | dB                |

|                                                                           |                                 |                                                    |                | 1          | 0    |      | 9.5               |      | ]                 |

|                                                                           |                                 |                                                    |                | 1          | 1    |      | 13                |      |                   |

|                                                                           |                                 | Source to IN                                       | OUT to load    | PE1        | PE0  |      |                   |      |                   |

|                                                                           |                                 |                                                    | 3m,<br>24 AWG  | 0          | 0    |      |                   |      |                   |

| Residual Output Deterministic<br>Jitter at 1.0Gbps<br>(Notes 4, 8, and 9) |                                 | 6-mil, 10in of FR-4                                | 5m,<br>24 AWG  | 0          | 1    |      |                   | 0.02 | UI <sub>P-P</sub> |

| (Notes 4, 8, and 9)                                                       |                                 |                                                    | 7m,<br>24 AWG  | 1          | 0    |      |                   |      |                   |

|                                                                           |                                 |                                                    | 10m,<br>24 AWG | 1          | 1    |      |                   |      |                   |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +3.0V \text{ to } +3.6V, T_A = 0^{\circ}\text{C to } +85^{\circ}\text{C}. \text{ Typical values are at } T_A = +25^{\circ}\text{C}, V_{CC} = +3.3V, \text{ unless otherwise noted.})$

| PARAMETER                                                                 | SYMBOL |                                                |                | MIN | TYP | MAX               | UNITS |      |                   |

|---------------------------------------------------------------------------|--------|------------------------------------------------|----------------|-----|-----|-------------------|-------|------|-------------------|

|                                                                           |        | Source to IN                                   | OUT to load    | PE1 | PE0 |                   |       |      |                   |

|                                                                           |        |                                                | 3m,<br>24 AWG  | 0   | 1   |                   |       |      |                   |

| Residual Output Deterministic<br>Jitter at 5.0Gbps<br>(Notes 4, 8, and 9) |        | 6-mil, 10in of                                 | 5m,<br>24 AWG  | 1   | 0   |                   | 0.09  | 0.12 | UI <sub>P-P</sub> |

|                                                                           |        | FR-4                                           | 7m,<br>24 AWG  | 1   | 0   |                   |       |      |                   |

|                                                                           |        |                                                | 10m,<br>24 AWG | 1   | 1   |                   |       |      |                   |

|                                                                           |        | Source to IN                                   | OUT to<br>load | PE1 | PE0 |                   |       |      |                   |

| Residual Output Deterministic<br>Jitter at 8.5Gbps<br>(Notes 4, 8, and 9) |        | 6-mil, 10in of<br>FR-4                         | 3m,<br>24 AWG  | 0   | 1   |                   |       |      |                   |

|                                                                           |        |                                                | 5m,<br>24 AWG  | 1   | 0   |                   | 0.15  | 0.20 | UI <sub>P-P</sub> |

|                                                                           |        |                                                | 7m,<br>24 AWG  | 1   | 0   |                   |       |      |                   |

|                                                                           |        |                                                | 10m,<br>24 AWG | 1   | 1   |                   |       |      |                   |

|                                                                           |        | Source to IN                                   | OUT to load    | PE1 | PE0 |                   |       |      |                   |

|                                                                           |        | 6-mil, 10in of                                 | 3m,<br>24 AWG  | 0   | 1   |                   |       |      |                   |

| Residual Output Deterministic<br>Jitter at 10Gbps<br>(Notes 4, 8, and 9)  |        |                                                | 5m,<br>24 AWG  | 1   | 0   |                   | 0.18  | 0.25 | Ul <sub>P-P</sub> |

| ( , , , , , , , , , , , , , , , , , , ,                                   |        | FR-4                                           | 7m,<br>24 AWG  | 1   | 1   |                   |       |      |                   |

|                                                                           |        |                                                | 10m,<br>24 AWG | 1   | 1   |                   |       |      |                   |

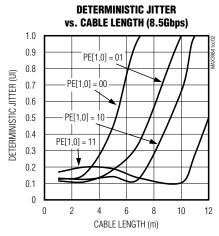

| Residual Output Deterministic<br>Jitter at 10.0Gbps                       |        | 10in of FR-4 at cable; see Figu                |                | PE1 | PE0 |                   | 0.10  |      | Ulp-p             |

| (Notes 4, 8, and 10)                                                      |        |                                                |                | 0   | 0   |                   |       |      |                   |

| Propagation Delay                                                         |        |                                                |                |     |     |                   | 230   |      | ps                |

| STATUS OUTPUT: LOS                                                        | T      | Inches de la constant                          | (5.1           |     |     |                   |       |      | 1                 |

| LOS Deassert                                                              |        | IN_LEV = high (Note 11)                        |                |     |     |                   |       | 300  | m\/= =            |

| LOS Assert                                                                |        | IN_LEV = low (Note 11) IN_LEV = high (Note 11) |                |     |     | 80                |       | 100  | mV <sub>P-P</sub> |

|                                                                           |        | IN_LEV = high (                                |                |     |     | 20                |       |      |                   |

| LOS Hysteresis (Note 4)                                                   |        | IN_LEV = Ingri                                 |                | 10  |     | mV <sub>P-P</sub> |       |      |                   |

### **ELECTRICAL CHARACTERISTICS (continued)**

(VCC = +3.0V to +3.6V, T<sub>A</sub> = 0°C to +85°C. Typical values are at T<sub>A</sub> = +25°C, V<sub>CC</sub> = +3.3V, unless otherwise noted.)

| PARAMETER                       | SYMBOL          | CONDITIONS                                                                                                                 | MIN | TYP | MAX  | UNITS |

|---------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------|-----|-----|------|-------|

| 10000-0000-000                  |                 | LOS asserted                                                                                                               | 0   |     | 25   | μΑ    |

| LOS Open-Collector Current Sink |                 | LOS asserted; V <sub>OL</sub> ≤ 0.4V                                                                                       | 1.0 |     |      | mA    |

| On it                           |                 | (Note 12)                                                                                                                  | 0   |     | 25   | μΑ    |

| LOS Response Time<br>(Note 4)   |                 | Time from V <sub>IN</sub> dropping below deassert level or rising above assert level to 50% point of LOS output transition |     |     | 10   | μs    |

| LOS Transition Time             |                 | Rise time or fall time (10% to 90%); pullup supply = 5.5V; external pullup $R \ge 4.7 k\Omega$                             |     | 200 |      | ns    |

| CONTROL INPUTS: TX_DISABL       | E, PE0, PE1     | , OUT_LEV, IN_LEV                                                                                                          |     |     |      |       |

| Logic-High Voltage              | V <sub>IH</sub> |                                                                                                                            | 2.0 |     |      | V     |

| Logic-Low Voltage               | VIL             |                                                                                                                            |     |     | 0.8  | V     |

| Logic-High Current              | Ιн              | Current required to maintain logic-high state at V <sub>IH</sub> > +2.0V                                                   |     |     | -150 | μА    |

| Logic-Low Current               | lıL             | Current required to maintain logic-low state at $V_{IL} < +0.8V$                                                           |     |     | 350  | μΑ    |

- Note 1: Supply voltage to reach 90% of final value in less than 100µs, but not less than 10µs. Power-on delay interval measured from the 50% level of the final voltage at the filter's device side to 50% level of final current. The supply is to remain at or above 3V for at least 100ms. Only one full-scale transition is permitted during this interval. Aberrations on the transition are limited to less than 100mV.

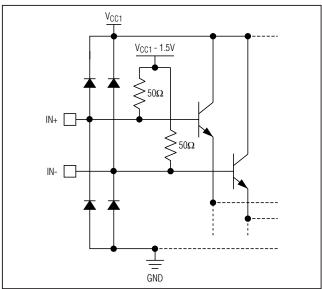

- **Note 2:** IN+ and IN- are single-ended,  $50\Omega$  terminations to (V<sub>CC</sub> 1.5V) ±0.2V.

- **Note 3:** Load is  $50\Omega \pm 1\%$  at each side and the pattern is 0000011111 or equivalent pattern at 2.5Gbps.

- **Note 4:** Guaranteed by design and characterization.

- Note 5: PE1 = PE0 = logic-high (maximum preemphasis), load is 50Ω ±1% at each side. The pattern is 11001100 (50% edge density) at 10Gbps. AC common-mode output is computed as:

$V_{ACCM\_RMS} = RMS[(V_P + V_N) / 2) - V_{DCCM}]$

#### where:

VP = time-domain voltage measured at OUT+ with at least 10GHz bandwidth.

V<sub>N</sub> = time-domain voltage measured at OUT- with at least 10GHz bandwidth.

AC common-mode voltage (V<sub>ACCM RMS</sub>) expressed as an RMS value.

DC common-mode voltage ( $V_{DCCM}$ ) = average DC voltage of ( $V_P + V_N$ ) / 2.

- Note 6: Using 00000111111 or equivalent pattern at 2.5Gbps. PE0 = PE1 = logic-low for minimum preemphasis. Measured within 2in of the output pins with Rogers 4350 dielectric, or equivalent, and ≥ 10-mil line width. For transition time, the 0% reference is the steady state level after four zeros, just before the transition, and the 100% reference level is the steady state level after four consecutive logic ones.

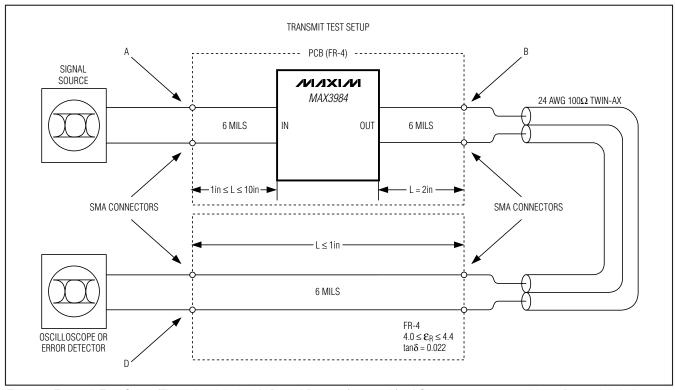

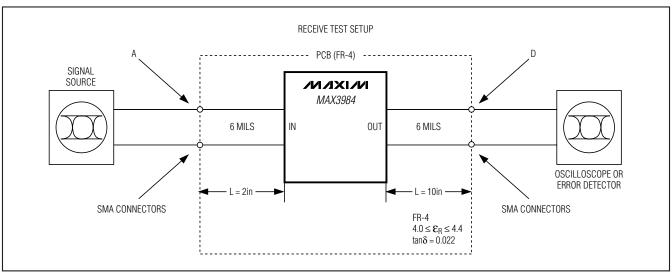

- Note 7: Pattern is 0000011111 or equivalent pattern at 10Gbps and 100mV<sub>P-P</sub> differential swing. IN\_LEV = logic-low and PE0 = PE1 = logic-low for minimum preemphasis. Signal transition time is controlled by the 4th-order BT filter (7.5GHz bandwidth) or equivalent. See Figure 3 for setup.

- Note 8: Test pattern (464 bits): 100 zeros, 1010, PRBS7, 100 ones, 0101, PRBS7.

- Note 9: Input range selection is IN\_LEV = logic-high for FR-4 input equalization. Cables are unequalized, Amphenol Spectra-Strip (160-2499-997) 24 AWG or equivalent. Residual deterministic jitter is the difference between the source jitter at point A and the load jitter point D in Figure 2. The deterministic jitter (DJ) at the output of the transmission line must be from media induced loss and not from clock source modulation. DJ is measured at point D of Figure 2.

- **Note 10:** Input range selection is IN\_LEV = logic-low. Residual deterministic jitter is the difference between the source jitter at point A and the load jitter point D in Figure 3. The deterministic jitter (DJ) at the output of the transmission line must be from media induced loss and not from clock source modulation. DJ is measured at point D of Figure 3.

- Note 11: Measured with 101010... pattern at 10Gbps with less than 1in of FR-4 at the input.

- **Note 12:** True open-collector outputs.  $V_{CC} = 0$  and the external  $4.7k\Omega$  pullup resistor is connected to +5.5V.

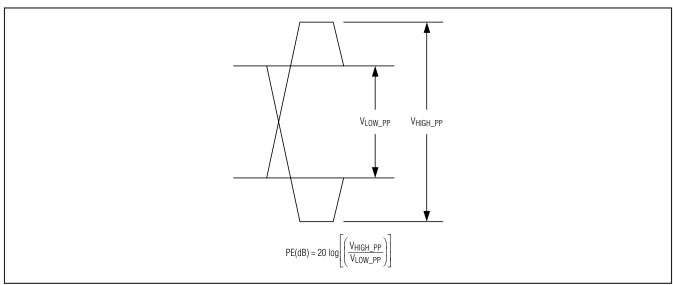

Figure 1. TX Preemphasis in dB

Figure 2. Transmit Test Setup (The points labeled A, B, and D are referenced for AC parameter test conditions. Deterministic jitter and eye diagrams measured at point D.)

Figure 3. Receive-Side Test Setup (The points labeled A and D are referenced for AC parameter tests.)

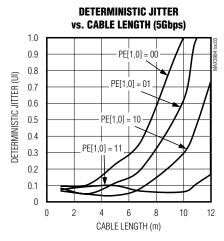

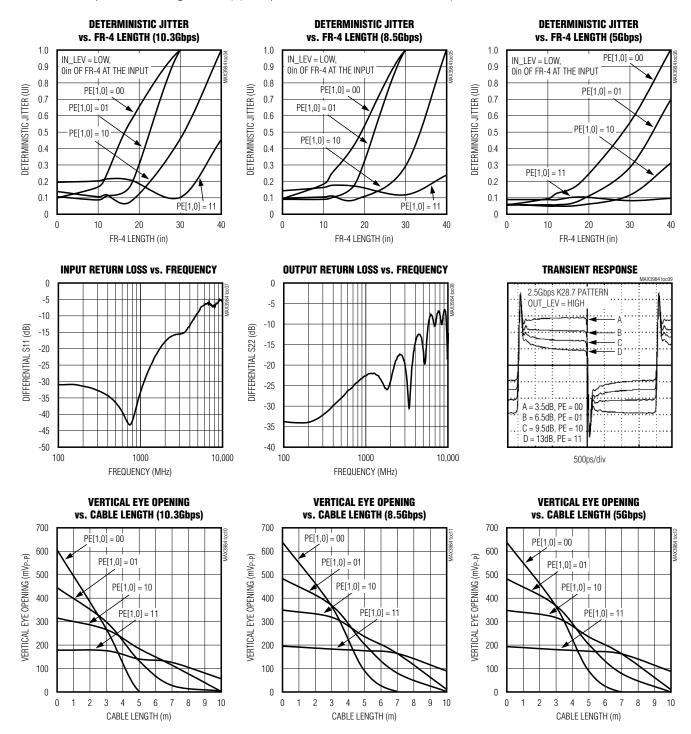

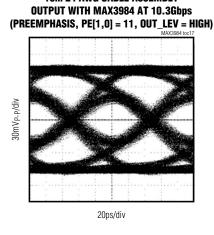

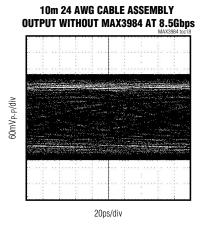

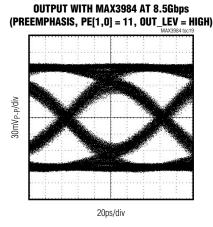

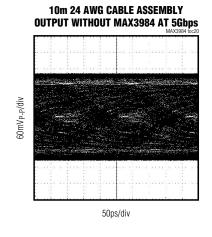

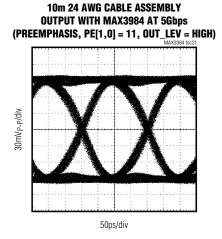

### Typical Operating Characteristics

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, PRBS7 + 100 CID pattern is PRBS 2^7, 100 zeros, 1010, PRBS 2^7, 100 ones, 0101, OUT_LEV = high, 10in of FR-4 at the input, IN_LEV = high, 360mV_{P-P} at input of FR-4, unless otherwise noted.)$

### Typical Operating Characteristics (continued)

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, PRBS7 + 100 CID pattern is PRBS 2^{7}, 100 zeros, 1010, PRBS 2^{7}, 100 ones, 0101, OUT_LEV = high, 10in of FR-4 at the input, IN_LEV = high, 360mV_{P-P} at input of FR-4, unless otherwise noted.)$

### Typical Operating Characteristics (continued)

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, PRBS7 + 100 CID pattern is PRBS 2^{7}, 100 zeros, 1010, PRBS 2^{7}, 100 ones, 0101, OUT_LEV = high, 10in of FR-4 at the input, IN_LEV = high, 360mV<sub>P-P</sub> at input of FR-4, unless otherwise noted.)$

10m 24 AWG CABLE ASSEMBLY

### **Pin Description**

| PIN         | NAME             | FUNCTION                                                                                                                                                                                                                                                  |

|-------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | V <sub>CC1</sub> | Power-Supply Connection for Inputs. Connect to +3.3V.                                                                                                                                                                                                     |

| 2           | IN+              | Positive Data Input, CML. This input is internally terminated with $50\Omega$ .                                                                                                                                                                           |

| 3           | IN-              | Negative Data Input, CML. This input is internally terminated with $50\Omega$ .                                                                                                                                                                           |

| 4, 8, 9, 16 | GND              | Circuit Ground                                                                                                                                                                                                                                            |

| 5           | OUT_LEV          | Output-Swing Control Input, LVTTL with $20k\Omega$ Internal Pullup. Set to TTL high or open for maximum output swing, or set to TTL low for reduced swing.                                                                                                |

| 6           | PE1              | Output Preemphasis Control Input, LVTTL with $10k\Omega$ Internal Pullup. This pin is the most significant bit of the 2-bit preemphasis control. Set high or open to assert this pin.                                                                     |

| 7           | PE0              | Output Preemphasis Control Input, LVTTL with $10k\Omega$ Internal Pullup. This pin is the least significant bit of the 2-bit preemphasis control. Set high or open to assert this pin.                                                                    |

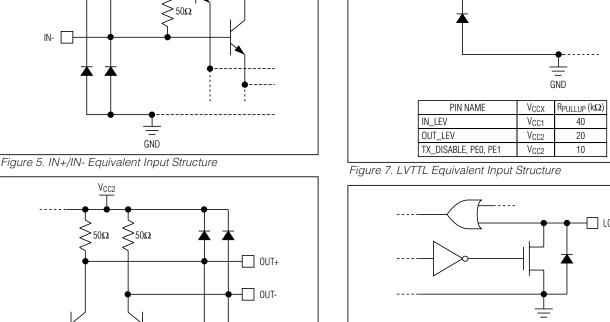

| 10          | OUT-             | Negative Data Output, CML. This output is terminated with $50\Omega$ to $V_{CC2}$ .                                                                                                                                                                       |

| 11          | OUT+             | Positive Data Output, CML. This output is terminated with $50\Omega$ to $V_{CC2}$ .                                                                                                                                                                       |

| 12          | V <sub>CC2</sub> | Power-Supply Connection for Output. Connect to +3.3V.                                                                                                                                                                                                     |

| 13          | TX_DISABLE       | Transmitter Disable Input, LVTTL with $10k\Omega$ Internal Pullup. When high or open, differential output is less than $10mV_{P-P}$ . Set low for normal operation.                                                                                       |

| 14          | LOS              | Loss-of-Signal Detect, Open-Collector TTL Output. Requires an external pullup $\geq$ 4.7k $\Omega$ (+5.5V maximum). This output sinks current when the input signal is above the LOS deassert level. To disable squelch pull LOS to ground.               |

| 15          | IN_LEV           | Receive Equalization Control Input, LVTTL $40k\Omega$ Internal Pullup. Set to TTL high or open for higher LOS assert/deassert levels and 10in FR-4 compensation. Set to TTL low for lower LOS assert/deassert levels and to bypass the FR-4 equalization. |

| _           | EP               | Exposed Pad. For optimal thermal conductivity, this pad must be soldered to the circuit board ground.                                                                                                                                                     |

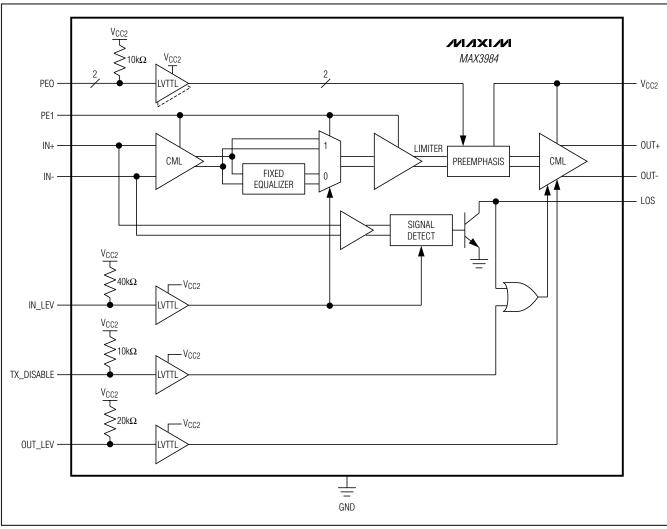

### **Detailed Description**

The MAX3984 is composed of a receiver, a driver, and an LOS detector with selectable threshold. Equalization is provided in the receiver. Selectable preemphasis and selectable output amplitude are included in the transmitter. The MAX3984 also includes transmit disable control for the output.

#### Receiver

Data is fed into the MAX3984 through a CML input stage and a selectable equalization stage. The fixed equalizer in the receiver corrects for up to 10in of PCB loss on FR-4 material at 10Gbps. The fixed equalizer can be bypassed by setting the IN\_LEV pin to a logic-low.

#### **Driver**

The driver includes four-state preemphasis to compensate for up to 10m of 24 AWG,  $100\Omega$  balanced cable, or 30in of FR-4. The OUT\_LEV pin selects the output amplitude. When OUT\_LEV is low, the peak-to-peak amplitude is 1000mVp-p. When OUT\_LEV is high, the peak-to-peak amplitude is 1200mVp-p.

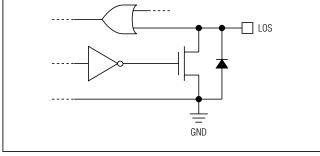

#### **Loss of Signal (LOS)**

Input LOS detection is provided. This is an open-collector output and requires an external pullup resistor ( $\geq 4.7 k\Omega$ ). The pullup resistors should be connected from LOS to a supply in the +3.0V to +5.5V range. The LOS output is not valid until power-up is complete.

\_\_\_\_\_\_\_/N/XI/W

Figure 4. Functional Diagram

The IN\_LEV pin sets the LOS assert and deassert levels. When IN\_LEV is LVTTL high or open, the LOS assert threshold is 300mV<sub>P-P</sub>. When IN\_LEV is LVTTL low, the LOS assert threshold is 100mV<sub>P-P</sub>.

TX\_DISABLE provides manual control for turning the output off. The MAX3984 has a squelch function that disables the output when there is an LOS condition. To disable the squelch function, connect LOS to ground (see the *Squelch* section).

### **Applications Information**

#### Squelch

The MAX3984 can automatically detect an incoming signal and enable or disable the data outputs. To enable squelch, the LOS pin must be connected to a TTL high or VCC with a pullup resistor ( $\geq 4.7 \text{k}\Omega$ ). Internally, TX\_DISABLE and LOS are connected through an OR-gate to control the CML outputs. The outputs are disabled if LOS asserts. To turn off the squelch function, LOS must be pulled to TTL low. The output can also be disabled when TX\_DISABLE is forced high.

#### Typical Characteristics at -40°C

The MAX3984 is guaranteed to work from 0°C to +85°C. Table 1 indicates typical performance outside the guaranteed limits.

Table 1. Typical Characteristics at -40°C

| PARAMETER                                                       | SYMBOL |                                                         | CONDITIO                                                                                           | NS          |         | MIN               | TYP | MAX               | UNITS              |  |

|-----------------------------------------------------------------|--------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------|---------|-------------------|-----|-------------------|--------------------|--|

|                                                                 |        | Figure 2; TX_DIS                                        | Measured differentially at point B in Figure 2; TX_DISABLE = low, OUT_LEV = high, PE1 = PE0 = high |             |         |                   |     | 1100              |                    |  |

| Different Output Swing (Note 1)                                 |        | Measured differe<br>Figure 2; TX_DIS.<br>OUT_LEV = low, | 920                                                                                                |             |         | mV <sub>P-P</sub> |     |                   |                    |  |

|                                                                 |        | TX_DISABLE = h                                          | igh, PE1 =                                                                                         | PE0 = hiç   | gh      |                   | 3.5 |                   |                    |  |

| Common-Mode Output (AC)                                         |        | Measured at poir TX_DISABLE = Io                        |                                                                                                    |             | Note 2) |                   | 5   |                   | mV <sub>RMS</sub>  |  |

| Random Jitter                                                   |        | Measured at poir                                        | nt D in Figu                                                                                       | ure 3 (Note | e 3)    |                   | 0.5 |                   | psrms              |  |

|                                                                 |        | Source to IN                                            | OUT to load                                                                                        | PE1         | PE0     |                   |     |                   |                    |  |

|                                                                 |        | 6-mil, 10in of<br>FR-4                                  | 3m,<br>24 AWG                                                                                      | 0           | 0       |                   |     |                   |                    |  |

| Residual Output Deterministic<br>Jitter at 1.0Gbps (Notes 4, 5) | 6      |                                                         | 5m,<br>24 AWG                                                                                      | 0           | 1       | 0.02              |     | Ulp₋p             |                    |  |

|                                                                 |        |                                                         | 7m,<br>24 AWG                                                                                      | 1           | 0       |                   |     |                   |                    |  |

|                                                                 |        |                                                         | 10m,<br>24 AWG                                                                                     | 1           | 1       |                   |     |                   |                    |  |

|                                                                 |        | Source to IN                                            | OUT to load                                                                                        | PE1         | PE0     |                   |     |                   |                    |  |

|                                                                 |        |                                                         | 3m,<br>24 AWG                                                                                      | 0           | 1       | 0.12              |     |                   |                    |  |

| Residual Output Deterministic<br>Jitter at 5.0Gbps (Notes 4, 5) |        | 6-mil, 10in of                                          | 5m,<br>24 AWG                                                                                      | 1           | 0       |                   |     | UI <sub>P-P</sub> |                    |  |

|                                                                 |        | FR-4                                                    | 7m,<br>24 AWG                                                                                      | 1           | 0       |                   |     |                   |                    |  |

|                                                                 |        |                                                         | 10m,<br>24 AWG                                                                                     | 1           | 1       |                   |     |                   |                    |  |

|                                                                 |        | Source to IN                                            | OUT to load                                                                                        | PE1         | PE0     |                   |     |                   |                    |  |

| Residual Output Deterministic<br>Jitter at 8.5Gbps (Notes 4, 5) |        |                                                         | 3m,<br>24 AWG                                                                                      | 0           | 1       |                   |     |                   |                    |  |

|                                                                 |        | 6-mil, 10in of<br>FR-4                                  | 5m,<br>24 AWG                                                                                      | 1           | 0       |                   | 0.2 |                   | UI <sub>P-</sub> P |  |

|                                                                 |        |                                                         | 7m,<br>24 AWG                                                                                      | 1           | 0       |                   |     |                   |                    |  |

|                                                                 |        |                                                         | 10m,<br>24 AWG                                                                                     | 1           | 1       |                   |     |                   |                    |  |

Table 1. Typical Characteristics at -40°C (continued)

| PARAMETER                                                      | SYMBOL | C                      | ONDITION       | NS SI |     | MIN  | TYP | MAX               | UNITS |

|----------------------------------------------------------------|--------|------------------------|----------------|-------|-----|------|-----|-------------------|-------|

| Residual Output Deterministic<br>Jitter at 10Gbps (Notes 4, 5) |        | Source to IN           | OUT to load    | PE1   | PE0 |      |     |                   |       |

|                                                                |        | 6-mil, 10in of<br>FR-4 | 3m,<br>24 AWG  | 0     | 1   |      |     |                   |       |

|                                                                |        |                        | 5m,<br>24 AWG  | 1     | 0   | 0.25 |     | UI <sub>P-P</sub> |       |

|                                                                |        |                        | 7m,<br>24 AWG  | 1     | 1   |      |     |                   |       |

|                                                                |        |                        | 10m,<br>24 AWG | 1     | 1   |      |     |                   |       |

**Note 1:** Load is  $50\Omega \pm 1\%$  at each side and the pattern is 0000011111 or equivalent pattern at 2.5Gbps.

Note 2: PE1 = PE0 = logic-high (maximum preemphasis), load is 50Ω ±1% at each side. The pattern is 11001100 (50% edge density) at 10Gbps. AC common-mode output is computed as:

$V_{ACCM} RMS = RMS[(V_P + V_N) / 2) - V_{DCCM}]$

#### where:

V<sub>P</sub> = time-domain voltage measured at OUT+ with at least 10GHz bandwidth.

V<sub>N</sub> = time-domain voltage measured at OUT- with at least 10GHz bandwidth.

AC common-mode voltage (VACCM RMS) expressed as an RMS value.

DC common-mode voltage  $(V_{DCCM})$  = average DC voltage of  $(V_P + V_N) / 2$ .

Note 3: Pattern is 0000011111 or equivalent pattern at 10Gbps and 100mVp-p differential swing. IN\_LEV = logic-low and PE0 = PE1 = logic-low for minimum preemphasis. Signal transition time is controlled by the 4th-order BT filter (7.5GHz bandwidth) or equivalent. See Figure 3 for setup.

Note 4: Test pattern (464 bits): 100 zeros, 1010, PRBS7, 100 ones, 0101, PRBS7.

Note 5: Input range selection is IN\_LEV = logic-high for FR-4 input equalization. Cables are unequalized, Amphenol Spectra-Strip (160-2499-997) 24 AWG or equivalent. Residual deterministic jitter is the difference between the source jitter at point A and the load jitter point D in Figure 2. The deterministic jitter (DJ) at the output of the transmission line must be from media induced loss and not from clock source modulation. DJ is measured at point D of Figure 2.

#### **Layout Considerations**

Circuit board layout and design can significantly affect the performance of the MAX3984. Use good high-frequency design techniques, including minimizing ground inductance and using controlled-impedance transmission lines on the data signals. Power-supply decoupling should also be placed as close as possible to the VCC pins. Always connect all VCC pins to a power plane. Take care to isolate the input from the output signals to reduce feed through.

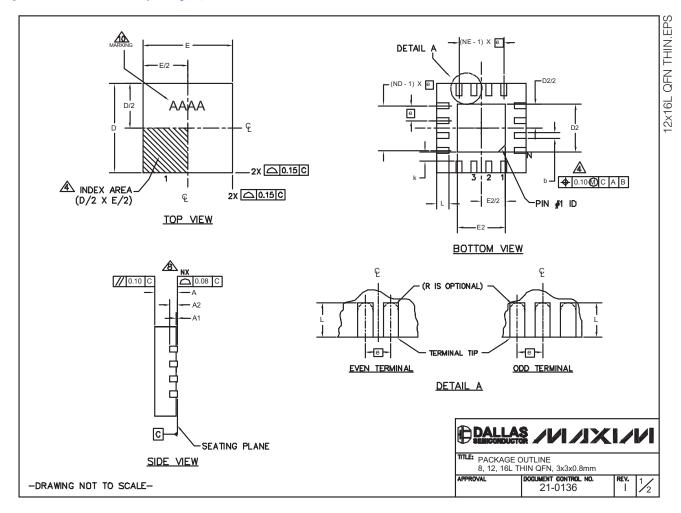

#### **Exposed-Pad Package**

The exposed-pad, 16-pin thin QFN package incorporates features that provide a very low thermal resistance path for heat removal from the IC. The exposed pad on the MAX3984 must be soldered to the circuit board for proper thermal performance. Refer to Maxim Application Note HFAN-08.1: Thermal Considerations of QFN and Other Exposed-Paddle Packages for additional information.

#### **Interface Schematics**

RPULLUP

LVTTL IN \_\_\_\_

Figure 6. OUT+/OUT- Equivalent Output Structure

Figure 8. Loss-of-Signal Equivalent Output Structure

Typical Operating Circuits (continued)

### **Pin Configuration**

Chip Information

PROCESS: SiGe Bipolar

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

| PKG  |           | 8L 3x3   |      | 1         | 12L 3x3  |      |      | 16L 3x3  |      |  |

|------|-----------|----------|------|-----------|----------|------|------|----------|------|--|

| REF. | MIN.      | NOM.     | MAX. | MIN.      | NOM.     | MAX. | MIN. | NOM.     | MAX. |  |

| Α    | 0.70      | 0.75     | 0.80 | 0.70      | 0.75     | 0.80 | 0.70 | 0.75     | 0.80 |  |

| b    | 0.25      | 0.30     | 0.35 | 0.20      | 0.25     | 0.30 | 0.20 | 0.25     | 0.30 |  |

| D    | 2.90      | 3.00     | 3.10 | 2.90      | 3.00     | 3.10 | 2.90 | 3.00     | 3.10 |  |

| Е    | 2.90      | 3.00     | 3.10 | 2.90      | 3.00     | 3.10 | 2.90 | 3.00     | 3.10 |  |

| е    | 0.65 BSC. |          |      | 0.50 BSC. |          |      | 0    | .50 BS   | Э.   |  |

| L    | 0.35      | 0.55     | 0.75 | 0.45      | 0.55     | 0.65 | 0.30 | 0.40     | 0.50 |  |

| N    |           | 8        |      |           | 12       |      | 16   |          |      |  |

| ND   |           | 2        |      |           | 3        |      |      | 4        |      |  |

| NE   |           | 2        |      |           | 3        |      |      | 4        |      |  |

| A1   | 0         | 0.02     | 0.05 | 0         | 0.02     | 0.05 | 0    | 0.02     | 0.05 |  |

| A2   | 0         | 0.20 REF |      |           | 0.20 REF |      |      | 0.20 REF |      |  |

| k    | 0.25      | -        | -    | 0.25      | -        | -    | 0.25 | -        | -    |  |

|           | EXPOSED PAD VARIATIONS |      |      |      |      |      |             |        |  |  |  |  |  |

|-----------|------------------------|------|------|------|------|------|-------------|--------|--|--|--|--|--|

| PKG.      | D2                     |      |      |      | E2   |      | PIN ID      | JEDEC  |  |  |  |  |  |

| CODES     | MIN.                   | NOM. | MAX. | MIN. | NOM. | MAX. | PINID       | JEDEC  |  |  |  |  |  |

| TQ833-1   | 0.25                   | 0.70 | 1.25 | 0.25 | 0.70 | 1.25 | 0.35 x 45°  | WEEC   |  |  |  |  |  |

| T1233-1   | 0.95                   | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-1 |  |  |  |  |  |

| T1233-3   | 0.95                   | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-1 |  |  |  |  |  |

| T1233-4   | 0.95                   | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-1 |  |  |  |  |  |

| T1633-2   | 0.95                   | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-2 |  |  |  |  |  |

| T1633F-3  | 0.65                   | 0.80 | 0.95 | 0.65 | 0.80 | 0.95 | 0.225 x 45° | WEED-2 |  |  |  |  |  |

| T1633FH-3 | 0.65                   | 0.80 | 0.95 | 0.65 | 0.80 | 0.95 | 0.225 x 45° | WEED-2 |  |  |  |  |  |

| T1633-4   | 0.95                   | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-2 |  |  |  |  |  |

| T1633-5   | 0.95                   | 1.10 | 1.25 | 0.95 | 1.10 | 1.25 | 0.35 x 45°  | WEED-2 |  |  |  |  |  |

#### NOTES

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

- THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO

JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED

WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR

MARKED FEATURE

- MIMENSION 6 APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.20 mm AND 0.25 mm FROM TERMINAL TIP.

- AND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- 7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- © COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- 9. DRAWING CONFORMS TO JEDEC MO220 REVISION C.

- MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

- 11. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

- 12. WARPAGE NOT TO EXCEED 0.10mm.

-DRAWING NOT TO SCALE-

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.